ロードマップでわかる!当世プロセッサー事情 第852回

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現

2025年12月01日 12時00分更新

2週ほど空いたが再びHot Chipsの解説に戻って、今回はGoogle TPU v7ことIronwoodを説明しよう。Google TPUについてはこれまでも何度か取り上げている。Google TPU v1~v3は連載565回で、v4は連載729回でそれぞれ触れている。

筆者以外の記事で言えば、TPU v5eはこちら、v5pはこちら、v6e(Trillium)はこちらで触れている。ややわかりにくいのでまとめると以下のようなる。

| Google TPUの歴史 | ||||||

|---|---|---|---|---|---|---|

| v1 | 2015年 初代 | 推論専用エンジン | ||||

| v2 | 2017年5月 | 推論/学習両対応。BF16のサポートを追加 | ||||

| v3 | 2018年5月 | v2の高性能版。最大1024チップまでスケール拡張 | ||||

| v4 | 2021年5月 | v3の性能をさらに向上。光スイッチを導入して大規模化を可能 | ||||

| v5e | 2023年8月 | v4のコストパフォーマンス向上版。同じコストであればv4の2倍の学習性能、2.5倍の推論性能を発揮するとする。ただしチップの絶対性能そのものはv4より低い | ||||

| v5p | 2023年12月 | v5eベースの高性能版。性能もv5e比で倍以上になり、より大量のチップを接続できる様になった。搭載メモリ量も拡大 | ||||

| v6e(Trillium) | 2024年5月 | v5e比で性能を4.7倍向上し、エネルギー効率も改善。ただし1つのPodは最大256チップ。v5eの後継といった位置づけ | ||||

v5世代はeとpの両バージョンがあり、Trilliumと命名方法が変わったv6世代もv6e相当だったので、次はv6pが来るのかと思っていたのだが、記事にもあるように今回のIronwoodはv7、つまり第7世代扱いとなっている。

このIronwood、今年11月25日にMetaがGoogleから数十億ドル規模で導入するとロイターなどで報じたことで俄然注目を集めるようになったわけだが、そんなIronwoodのもう少し細かな部分がHot Chipsで紹介された。

Ironwoodのピーク性能はBlackwellの半分ほど

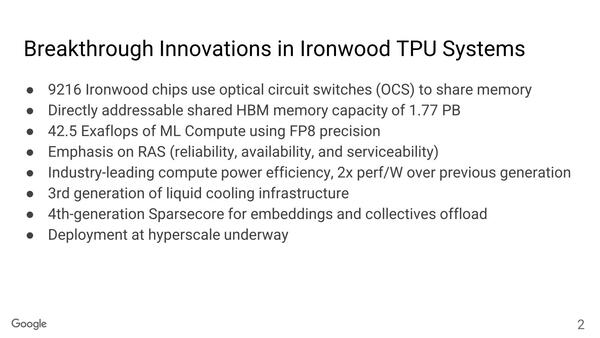

まずIronwoodの主要な特徴が下の画像だ。ここでの数字は、Googleの言うPod(9216コアを集積したサーバーラック群)での数字なので、チップあたりの容量はもっと少なくなるのだが、それにしてもなかなか意欲的である。

9216チップで42.5EFlopsなので、チップあたり4.6PFlopsほど。BlackwellがFP8で1枚あたり9PFlops(Tensor Core)とされるので、ピーク性能の比較で言えばざっくりBlackwellの半分ほどとなる

8bit精度というのは初代のTPUからのもはや伝統という感じで、今後FP4などに移行するつもりかどうかはよくわからないが、このあたりはGoogleのこだわりなのかもしれない。

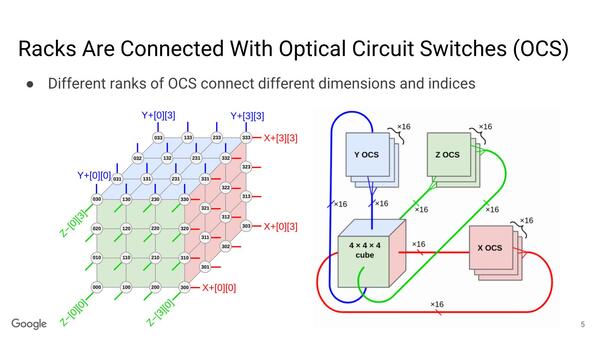

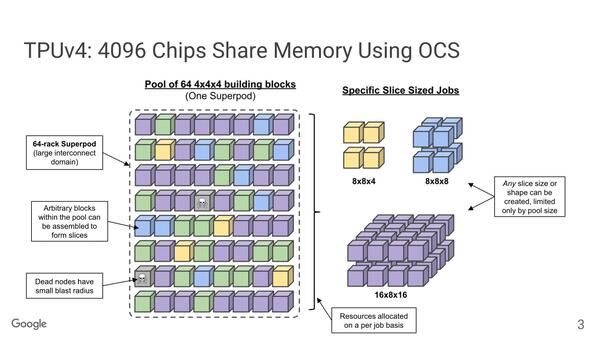

Superpodという名称はNVIDIAも使っているが、TPU v4世代では最大4096個のチップをまず64個ずつのキューブとし、このキューブを組み合わせて複数のJobを走らせるという形になっていた。

ここで出てくるOCSとは連載729回に出てきたOptical Circuit Switchのことである

これがTPU v5p世代では8192チップ(64×8×16)に増えていたが、Ironwoodでは64×9×16=9216チップに増強された。

キューブ同士は3次元トーラス構造になっているが、肝心のトーラスがX/Y/Zにいくつつながっているのか、は不明である(図はTPU v4世代と同じままである)。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ