ロードマップでわかる!当世プロセッサー事情 第847回

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手

2025年10月27日 12時00分更新

1チップで50TFlopsを達成予定の最新プロセッサーPEZY-SC4s

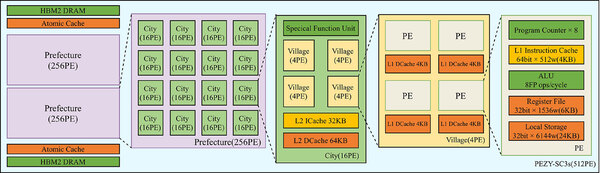

ここまでの話はPEZY-SCシリーズ全部に共通する話だが、ここからはSC4sの実装の話となる。PEそのものの構造は変わらない。

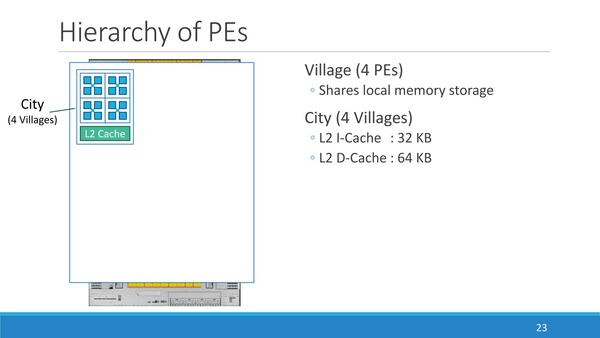

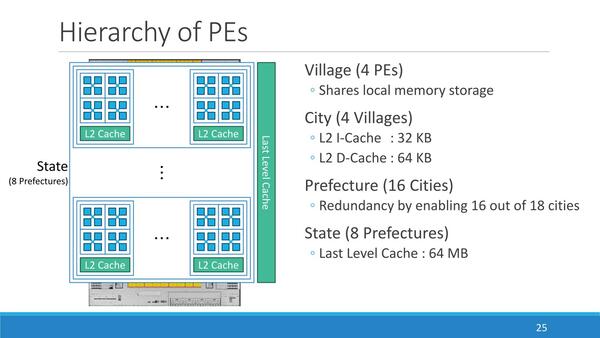

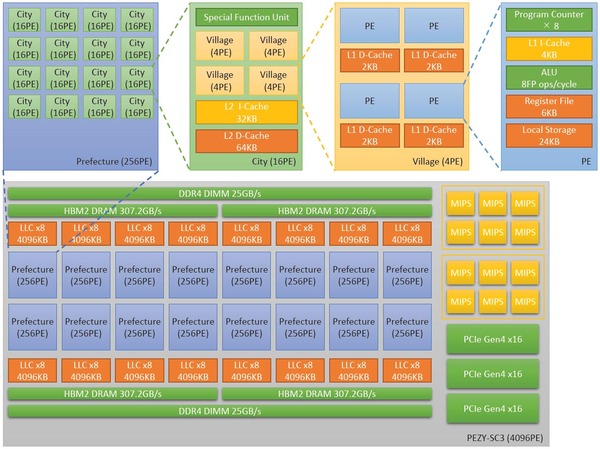

このPEを4つ集めたものをVillageと呼び、そのVillageを4つまとめたものをCityと呼ぶ。このCityには追加でL2 I-CacheとL2 D-Cacheが搭載される。

そのVillageを16個まとめたのがPrefecturesと呼ぶのだが、実際にはここで冗長Cityが2つ搭載されており、物理的には18 Cityで1 Prefectureを構成している。

PEZY-SC4sがPEZY-SC3と異なるのはここからで、PEZY-SC4sは8 PrefectureでStateを構成しており、このStateに64MBのLLCが搭載されている。ところがPEZY-SC3では16 PrefectureでStateが構成されており、そこに64MBのLLCが搭載されていた。

さらに言えばPEZY-SC3sでは2 PrefectureでStateが構成されている。したがってPEZY-SC4sの性能はPEZY-SC3の半分程度でないとおかしいのだが、実際にはPEZY-SC3を上回る性能となっている。

Photo14がPEZY-SC3sまでのPEの内部構造であり、整数レジスターは64bit、浮動小数点は128bit SIMD構成でそれぞれ32個づつ搭載される。ALUで浮動小数点演算も可能であり、64bit倍精度ならALU1つ当たり2FLOP/サイクル、これが2つあるので4FLOP/サイクルという計算になる。

実際計算してみると、PEZY-SC3では実質3.2FLOP/サイクルほどになるが、これはメモリー不足に足を引っ張られている可能性が高い。対してPEZY-SC4では8.0FLOP/サイクルになっており、かといってALUを4つにしているとも思えないので、おそらくSIMDレジスタが256bit化されたものと思われるのだが、このあたりの詳細は今回公開されていない。

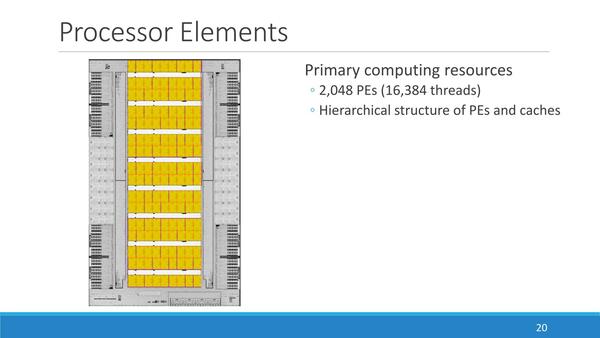

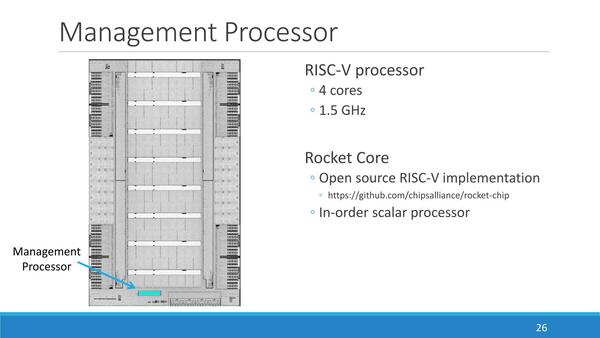

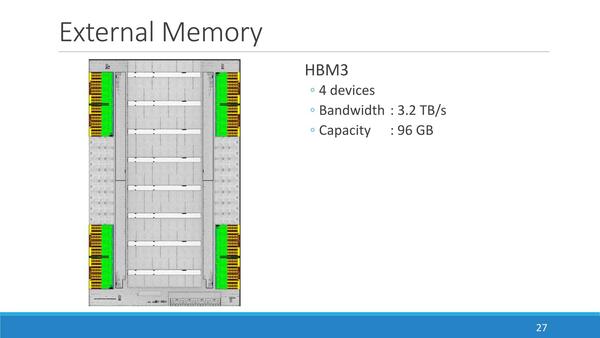

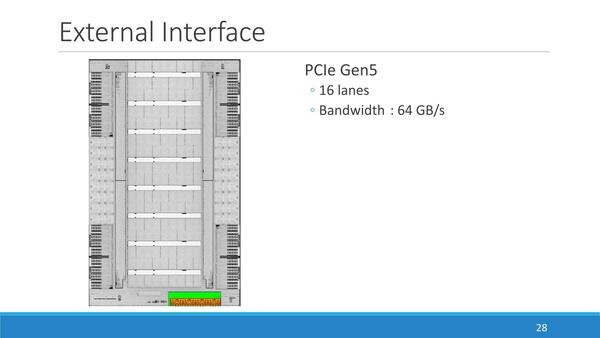

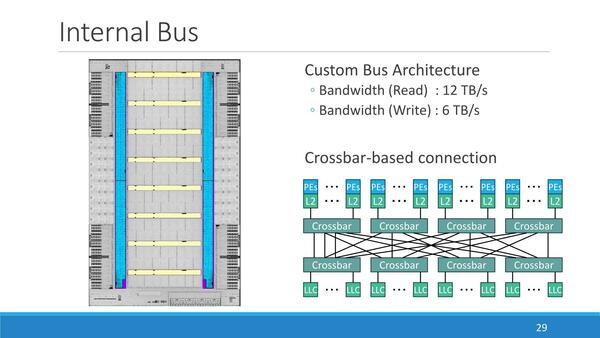

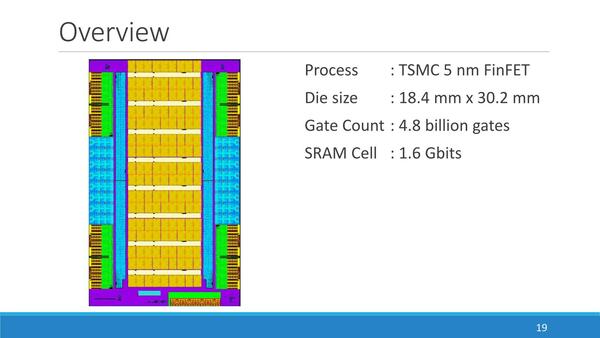

このPE(というかState)がチップの大半を占めており、他にマネジメント・プロセッサー、HBM3×4、PCIe Gen5×16、インターナル・バスなどが詰まっている。最終的なダイサイズは555.68mm2ほどになっている。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ