VLSIシンポジウム解説の4回目は、JFS(Technology / Circuits Joint Focus Session)1-1として行なわれたGlobalFoundries(GF)の"Key Technologies and Performance Aspects for Electrical and Optical Interconnects"という招待講演の内容を取り上げたい。

激化するSilicon Opticsの製造競争

Silicon Opticsが急に注目を浴びている。この分野では昨年のHot ChipsにおけるインテルとBroadcomの発表を紹介したが、他にもMarvellや最近ではSTMicroelectronicsも参入している。

ただ早くから参入していたという意味ではTSMCも欠かすことはできず、2021年にCOUPE(COmpact Universal Photonic Engine)を発表し、2024年から顧客への提供を開始した。そしてその顧客の一社がNVIDIAであり、今年そのCOUPEベースのチップが出荷予定となってる。

そういえばこのTSMCのSilicon Opticsの話は全然していなかったので、いずれどこかでしたいと思うのだが、そのTSMCの向こうを張るように本格的に参入を決めているのがGFである。

GFは2022年、Fotonixという名称で第1世代のSilicon Photonicsプラットフォームを発表する。このFotonixの発表には、Broadcom、Cisco、MarvellとNVIDIAに加え、Ayar LabsやLightmatter、PsiQuantum、Ranovus、Xanaduといったメーカーが名前を連ねていた。

Lightmatterの名前が出ているあたりは連載676回で紹介したEnviseやPassageの製造がGFだったことを示唆するものだし、BroadcomやMarvellはあくまでFablessの会社であり、これらの会社のSilicon Opticsコンポーネントの製造そのものはGFであった可能性を示唆するものだ。

GFは今年3月、第2世代のFotonixを発表している。これに先立ち今年1月17日には、ニューヨーク州マルタにAdvanced Packaging and Photonics Centerを建設することを発表した。

Advanced Packaging and Photonics Centerへの総投資額は5億7500万ドルで、さらに今後10年の間に研究開発向けに最大1億8600万ドルの追加投資の計画もある。また、今年6月4日にはニューヨーク州及びバーモント州の設備での半導体およびパッケージング製造能力向上のため、160億ドルの投資を発表した。このパッケージング製造能力にはSilicon Opticsも含まれており、要するにSilicon Optics周りの製造能力強化に向けてGFはアクセルを床まで踏み込んだ状況になっているわけだ。

最短の配線長で、より高い帯域を低消費電力で実現できるCPO

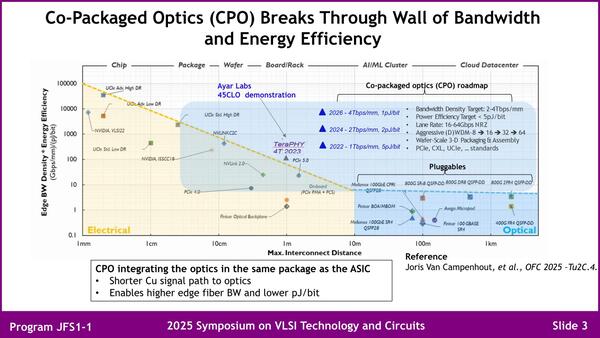

ということで、簡単にバックグラウンドを説明したうえで講演の内容である。まずCPO(Co-Package Optics)の大まかなロードマップが下の画像だ。縦軸は速度(厳密には単位消費電力あたりの速度)、横軸が到達距離であり、黄色いエリアが電気信号、水色が光信号だ。重なっている部分は、現在は電気信号ベースだが将来は光信号になる可能性がある部分である。

さて、CPOとはなにか? というGFの回答が下にある「OpticsをASIC内のパッケージに収めること」であり、この結果として銅配線(=電気配線)の長さを最小にでき、より高い帯域を低い消費電力で実現できる、としている。このあたりは他のメーカーも大体同じなのだが、右上にあるロードマップがおもしろい。

2022年は1Tbps/mmで5pJ/bit程度なのが、2024年には2Tbps/mmで2pJ/bit、2026年は4Tbps/mm、1pJ/bitになるというか、したいという目標だ。最初の数字は要するに、幅1mmに収まるFiberでどれだけの転送速度を実現できるかという話、後者はエネルギー効率の話である。

もっともエネルギー効率を考える場合、到達距離がどれだけかという議論が避けて通れない。これは光イーサネットの世界も同じで、都市間接続に使われる到達距離100Km台の規格と、データセンター内で使われる到達距離500m以下の規格では、そもそも光出力そのものが異なってくるからだ。ロードマップのものはおそらく到達距離10m未満(下手をすると1m未満)ではないかとは思うのだが。

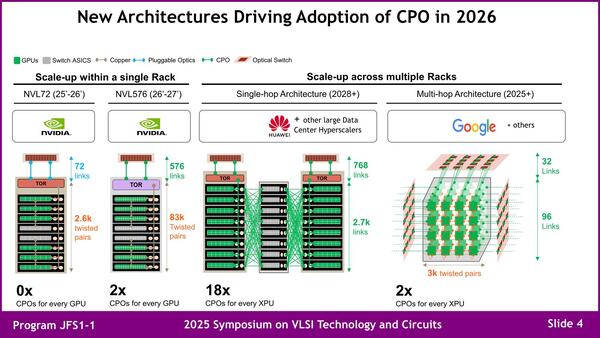

そのCPOについて、すでに公表されているCPOを利用したシステムというのが下の画像だ。NVIDIAは今年発売予定のSpectrum-XでCPOを採用することをすでに発表済であり、またGoogleも2023年の時点でネットワークが光化されていることは連載729回で説明したが、この先にCPOを使うことがほぼ確実視されている。

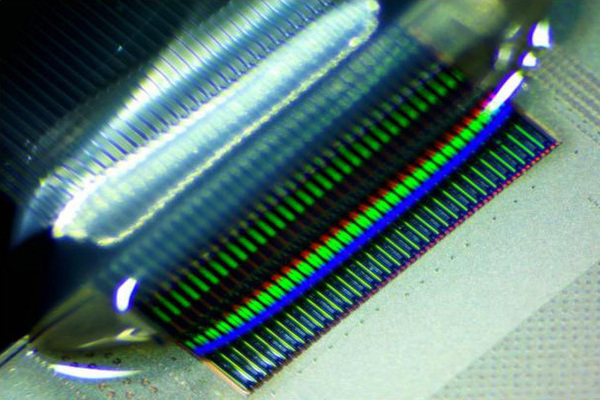

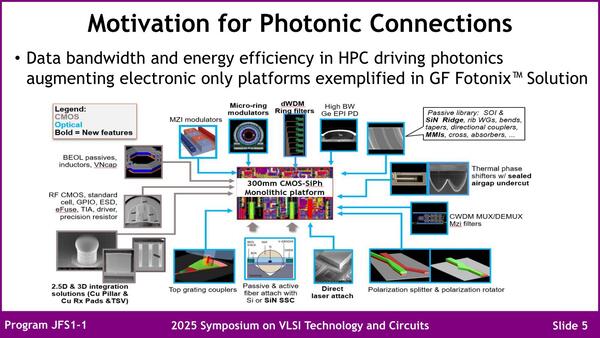

こうしたCPOを支えるコンポーネントとして、すでにGFのForonixではさまざまなコンポーネントが提供されているとする。

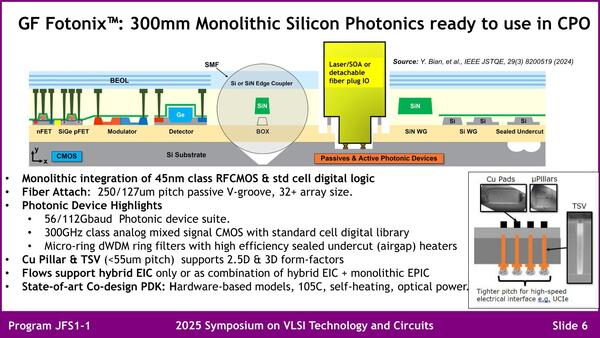

GFのFotonixのメリットは、これを300mmの45CLO : 45nm RF SOI CMOSで構築できることである。45nmというのは微妙なところで、光信号の制御や調整などのデジタル回路を積層するのには十分な速度ではあるのだが、例えばUCIeのI/F(現在だと最大32Gbps)を構築するには明らかに性能が足りない。

GFのFotonixは、300mmの45mm RFCMOSプロセスで構築できる。ちなみにこの45nm RFCMOSはSOIベースである。TSMCもSOIウェハーを利用しており、CPOにはSOIの方が有利なようだ。ただSOIを使わないインテルのような例もあるので、SOIが必須というわけではない

したがって、FotonixはあくまでもOptical側のコンポーネントに留められており、これをもっと高速なプロセスで製造した電気側のI/F(EIC:Electric IC)と接続するような構成を取ることになる。右下にTSVを使って高密度の接続が可能という説明があるが、現実問題としてはEICとこのFotonixベースのPIC(Photonic IC)をTSV経由で3D積層するといった形の実装になるかと思われる。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ