今回は、VLSIシンポジウムでインテルが招待講演として語った"Beyond RibbonFET: Energy Efficiency Innovations to Drive Technology and Design for the Next Decade"(TFS2-2)の内容を説明する。

Intel Foundryとしての提供がどうなるか、はともかくとして一応Intel 18Aはほぼ完成して、Panther Lakeの量産に向けて準備を整えるとともに、Intel 14Aの実用化に向けての作業も行なっているものと思われる(Intel 18A-PとIntel 18A-PTは、正直この先どうなるのか見えなくなっている。やるとしても優先度が下がりそうな感じだ)。今回の講演は、そのIntel 14Aのさらに先の話である。

プロセッサーが抱える現状の課題は

消費電力削減とトランジスタの小型化

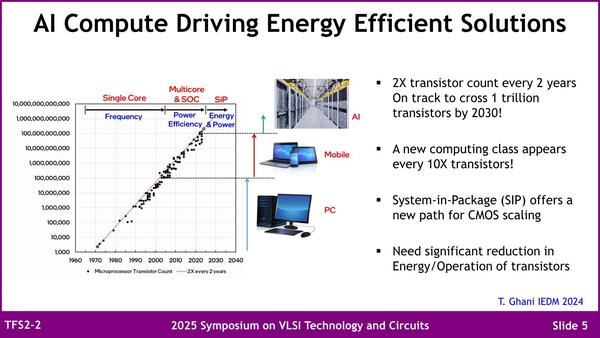

昨今AI Eraなどと呼ばれるようになっており、AIプロセッサーに利用されるシステムの消費電力が大問題になっているのは御存じのとおり。

昨今では動作周波数を引き上げるのはだいぶ難しくなっており、むしろ演算器の数を増やす方向になっていて、それもあって世代ごとに必要となるトランジスタの数が10倍になるという状況になっている。特にAIでは並列処理が効果的に動くため、演算器の数にスケールするように性能が上がりやすいからだ。こういう状況であるから、消費電力を減らせないにしても増え方を抑えるためには、まずトランジスタの消費電力を下げるというか、より効率的にする必要があると説く。

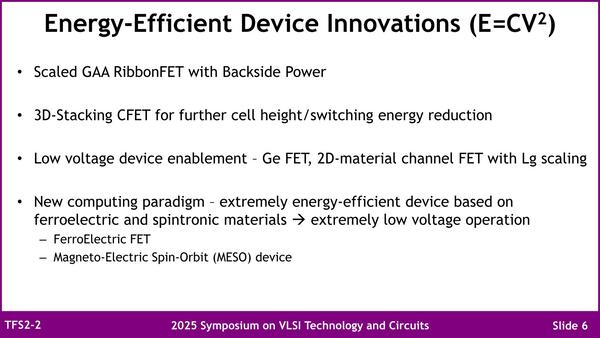

このための基本的な構造は現在のGAA RibbonFETにBSPDNを組み合わせた形の進展で実現できるが、ただしその先には新材料や根本的に新しいデバイスが必要であるとする。

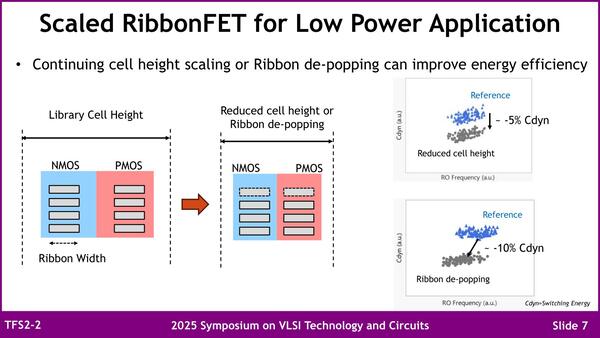

さて近未来、おそらくIntel 14Aの次か次の次くらいに来るであろう話が、トランジスタの小型化である。これはRibbonの幅を減らすことでCell Heightそのものを削減するとともに、Ribbonの数を減らすことで、それぞれCdyn(dynamic effective capacitance)を5%/10%削減できるとする。Cdynは要するにトランジスタが動作している時の、見かけ上の容量と見なせる。

このCdynがなぜ重要か? というと、動作に必要なエネルギーE=C×V<sup>2</sup>として計算できるため、Cdynを減らすとそれだけエネルギーが削減できるからだ。もちろん動作電圧を下げる方がより効果的ではあるが、電圧を減らすのは前提として、さらに下げようと思うと容量を小さくした方がいい。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ