ロードマップでわかる!当世プロセッサー事情 第814回

インテルがチップレット接続の標準化を画策、小さなチップレットを多数つなげて性能向上を目指す インテル CPUロードマップ

2025年03月10日 12時00分更新

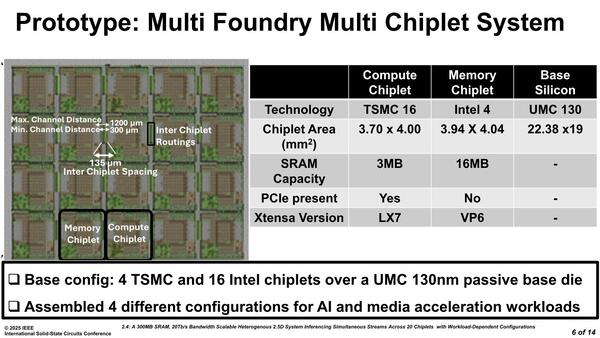

コンピュートタイルはTSMC N16、メモリータイルはIntel 4

ベースタイルはUMCの130nmプロセスを利用

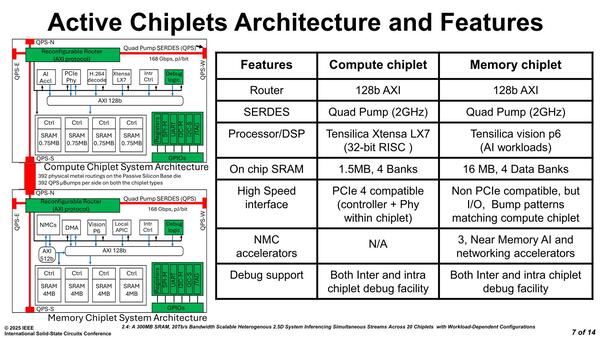

下の画像が実際のタイルの細かい構成である。コンピュートタイルのCPUコアとしてはTensilicaのXtensa LX7が、AIエンジンのコアにはXtensa VP6(Vision P6)がそれぞれ採用されている。メモリータイルはAI処理をさせることもあってか16MBのSRAMが搭載されている。

タイルの構成。メモリータイルはAI処理をするのにメモリーがそれなりに必要であり、それもあって16MBのSRAMを搭載している関係でメモリータイル呼ばわりされているが、本来はアクセラレータータイル扱いにすべきではないのだろうか?

おもしろいのはコンピュートタイルはTSMC N16で製造していることで、一方メモリータイルはIntel 4、そしてベースタイルはUMCの130nmプロセスを利用したものだ。ベースタイルは本当にパッシブタイルで純粋に配線だけがされているようだ。

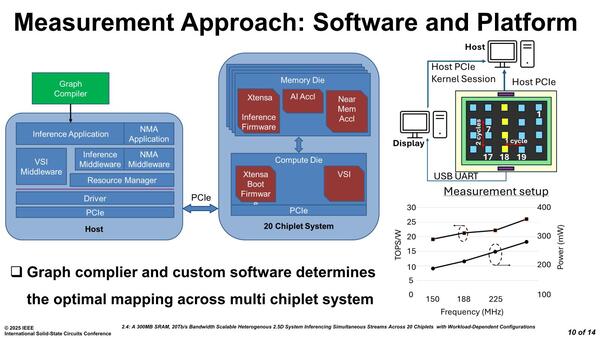

コンピュートタイルとメモリータイルのもう少し詳細な内部構造が下の画像だ。コンピュートタイルにはPCI Express Gen4のコントローラに加えてPHYまで搭載されているとする。デバッグロジックを新規で開発したのは、複数のタイルで連動して動くような処理のデバッグは、Xtensa LX7に用意されている通常のデバッグ機能だけでは足りなかったのだろうと想像される。

またコンピュートタイルに搭載された3MBのSRAMはXtensa LX7 coreを含む128bit AXIの内部バスからのアクセスだけを想定しているが、メモリータイルに搭載されている方は外部のネットワーク経由で直接アクセスすることも想定しているのか、NMC(Near Memory Controller)と呼ばれるアクセラレーターを3基持ち、しかもそのNMCとメモリーの間が512bitのAXIバスでつながっているあたりが、使われ方の違いを表している。

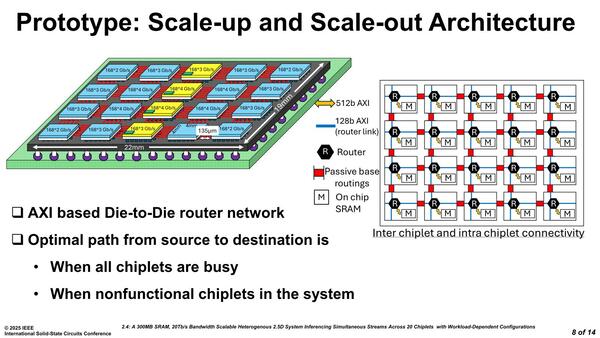

下の画像が実際のプロトタイプの構成である。5×4で20個のタイルが搭載されるが、うちコンピュートタイルが16個、メモリータイルが4つである。

チップレット同士の間隔は135μmであるが、D2DのPHYは必ずしも4辺にあるわけでなく偏りが見られる。この関係で実際の配線長は、短いもので300μm、長いもので1200μmになる。この配線への制御は各タイルに置かれたルーターが制御する格好になり、チップ内部的には128bit AXIでこれをつないでいる格好らしい。

ところで上の画像の右側を見ると、すべてのタイルでSRAMとルーターが512bit AXIで接続されているようにみえるが、2つ上の内部構造画像では512bit AXIを持つのはメモリータイルだけになっている。

どちらかが間違ってるわけで、なんとなく2つ上の内部構造画像の方がSRAMの接続部に512bit AXIを書き忘れている気もしなくもないが、その512bit AXIの駆動にNMCが必要ということを考えると、上の画像の右図が間違っているようにも思える(2つ上の画像の表に、コンピュートタイルにはNMCアクセラレーターがない、と明記してあるあたりこれは間違いなさそうだ)。

それはともかくとして、このタイル間の接続は1方向あたり168Gbpsになっている。四隅のタイルは168Gbps×2、各辺に配されたタイルは168Gbps×3、そして中にあるタイルは168Gbps×4の帯域を持つことになり、これを合計すると168×(2×4+3×10+4×6)=168×62=10416Gbps。実際にはこれが双方向なので、トータルで20Tbpsとなり、これがタイトルの"20Tb/s Bandwidth"につながるわけだ。

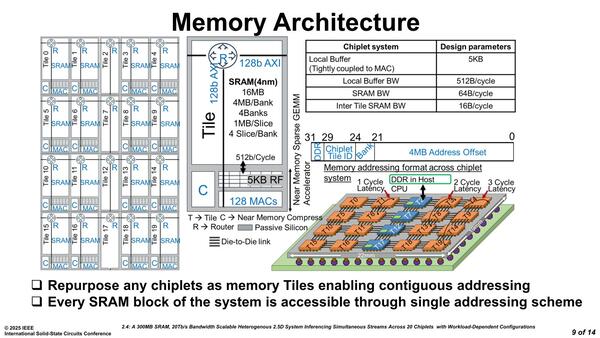

メモリータイルの内部構造が下の画像である。実際には1MBのスライスが4つで1つのバンクを構成、これが4バンクで16MBとなる。

AIエンジン用のレジスターファイルとは512bit/サイクルで接続され、128MACのAIエンジンはこのレジスターファイルを使って処理する。同時にこの16MBのSRAMにはグローバルアドレスが付加されておりこれを利用してXtensa LX7 coreからアクセスすることも可能という仕組みだ。

さすがにこれ単独で動作させるのは難しいので、アプリケーションを実際に走らせる際にはホストが必要になっている。その意味では、これ全体でアクセラレーターみたいなものである。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ