Granite Rapidsのダイサイズは

PHYまで含んでほぼ600平方mm

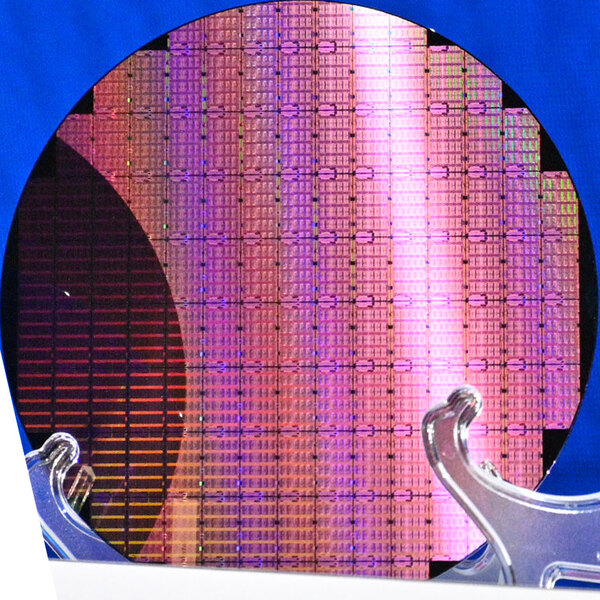

ところで今回の基調講演、壇上には展示されていながら説明されなかったのがGranite Rapidsのウェハーである。

これをむりやり歪み補正したのが下の画像だ。ダイサイズは32.18×18.65mmで599.98mm2なので、ほぼ600mm2となる。

連載736回ではコア部だけで600mm2程度、周辺のPHYも合わせると700mm2を切る程度と想定したが、実際にはPHYまで含んで600mm2以内に収まった格好だ。

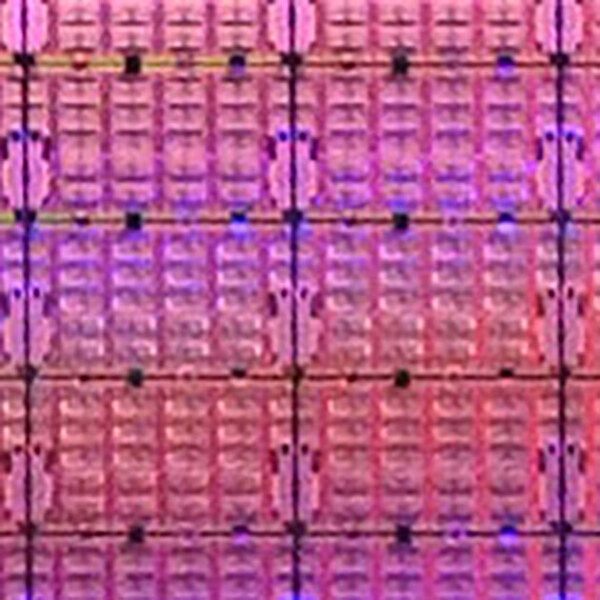

Granite Rapidsのウェハー中央部を切り抜いたのが下の画像で、縦方向に5本、横方向に6本のメッシュが通っているように見える。

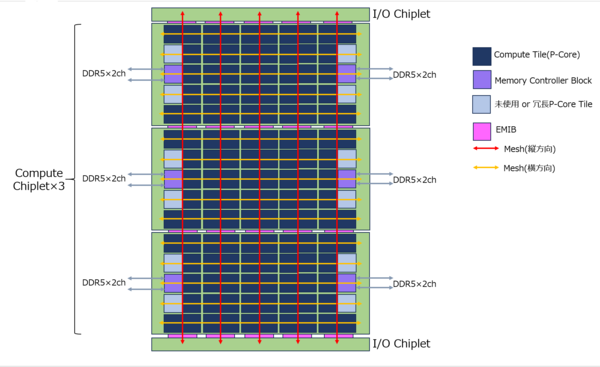

連載736回でGranite Rapidsの内部構造の想像図を掲載したが、その図は間違っていた。

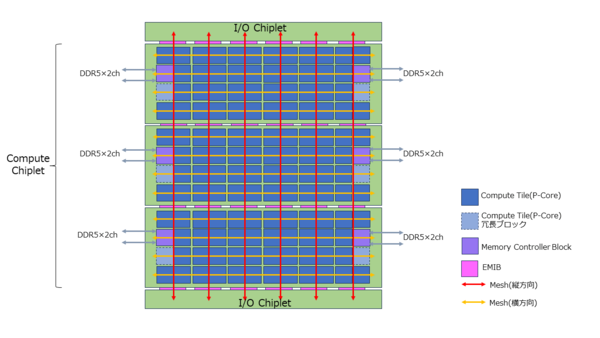

この図ではコンピュート・チップレットあたり縦方向6本、横方向5本のメッシュを想定していたが、実際の構成は下図になると想像する。

ちなみにこれは最大構成の3コンピュート・チップレットの場合で、この下に2コンピュート・チップレットで8ch DDR5の構成や、1コンピュート・チップレットで同じく8ch DDR5(これのみチップレット構成そのものが異なる)が用意されると思われる。

余談だが、そのGranite RapidsとSierra Forest、それとSierra Forestの後継となるClearwater Forestの3つの製品に関しては、正式に新しいBirch Stream Platformを使うことが明確にされた。

Sapphire Rapidsの提供が遅れたことで、Eagle Stream Platformは1年かそこらしか使われないのは少し可哀想である。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ