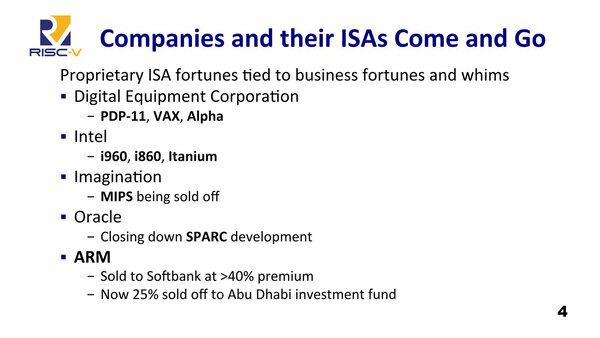

要するにx86やArmはどちらにしても論外なのだが、では他は? というと、どれもイマイチである。

Alphaの命令セットライセンスはおそらくHP(HPE)が保有しているはずだが、それをライセンスしたという話は聞かない。歴史的に言えばSamsungとCOMPAQが共同出資したAPL Networks(旧称Alpha Processor Inc.)にライセンスされたが、そのAPL Networksが解散した後、たしかHPが命令セットの権利を引き続き保有しているはずである

いまさらAlphaはないし、インテルのi860やi960、Itaniumとかも話にならない。MIPSは「RISC-Vの後」にOpen MIPS Initiativeなる取り組みを始めたものの、あっという間に終了。MIPS Technologyは現在RISC-Vアーキテクチャーを開発しており、もうMIPSは顧みていない。一応MIPSの命令セットライセンスは2010年時点では取得できたが、(1)と(2)には制限がある。

SPARCはOpenSPARCが存在するので一応利用は可能だが、(1)と(2)が引っかかる。OpenPOWERはもう少し後の2013年に設立されたが、この頃にはPower.orgという組織がPowerPCの命令セットをライセンスしていたはずである。

ただこれも(1)と(2)が引っかかる。つまり、商用プロセッサーの命令セットを使う、というアイディアは上手くなかったわけだ。

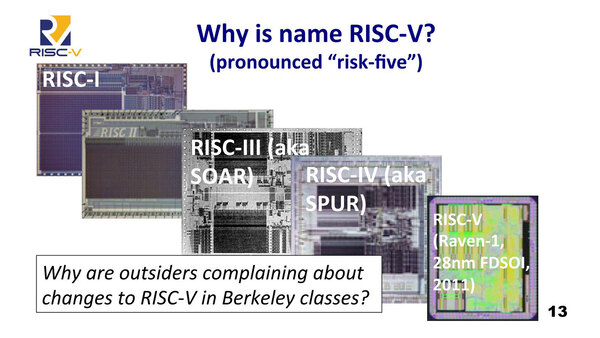

ではどうしたか? というと、自前で作ることにしたわけだ。そもそもなぜRISC-Vと名付けられたか?というと、UCBではそれまでに4世代のRISCプロセッサーを自前で開発していた。

もともと同じUCBのDavid Patterson教授(UCBの名誉教授兼RISC-V International副会長)が1982年にRISC-Iを開発している。Berkeley RISCという名称の方が有名かもしれないが、Sun MicrosystemsのSPARCプロセッサーの基になったプロセッサーであり、スタンフォード大のJohn LeRoy Hennessy教授(元スタンフォード大学長、現在はGoogle親会社であるAlphabetの会長)が開発したStanford MIPSと並ぶ、RISCプロセッサーの源泉でもある。

正確に言えば、まずBerkeley RISCが開発され、これをさらに洗練させて実用的なプロセッサーに仕立てたのがStanford MIPSというべきか。ただStanford MIPSはその後MIPS Computer SystemsによってR2000という商用プロセッサーになったのに対し、Berkeley RISCはこの改良型であるRISC IIまで開発されたものの、あくまでも研究用の試作に留まっており、SPARCを始めとするほかのプロセッサーに影響は与えたものの、このままで商用化はなされていない。

次のRISC-III(SOAR)はRISC-IIをベースにSmalltalkという言語を実行させるためにカスタマイズしたバージョン、RISC-IV(SPUR)は同じくRISC-IIをベースにしながら、マルチプロセッサーのワークステーションを構築するためのプロセッサーである。この4つのプロセッサーはいずれもPatterson教授が直接的に係わっている。

余談だが、そのPatterson教授とHennessy教授の有名な著作がComputer Architecture: A Quantitative ApproachとComputer Organization and Designの2冊の著作(どちらも日本語版も存在する)である。

■Amazon.co.jpで購入

-

コンピュータアーキテクチャ[第6版]定量的アプローチジョン L ヘネシー、デイビッド A パターソン、発行:エスアイビー・アクセス 発売:星雲社、中條 拓伯、天野 英晴、鈴木 貢星雲社

■Amazon.co.jpで購入

-

コンピュータの構成と設計 MIPS Edition 第6版 上David Patterson、John Hennessy、成田 光彰日経BP

■Amazon.co.jpで購入

-

コンピュータの構成と設計 MIPS Editoin 第6版 下David Patterson、John Hennessy、成田 光彰日経BP

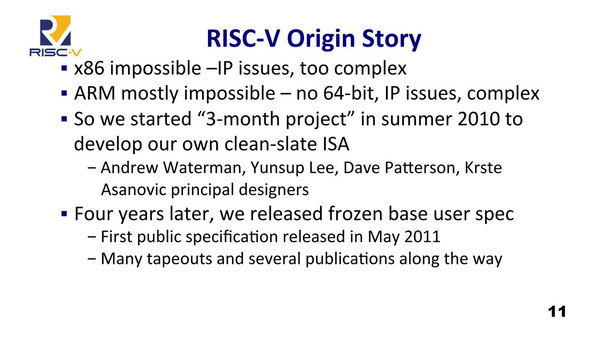

さて話をRISC-Vに戻すと、Asanović教授は自前で独自の命令セットを構築し、それをベースにしたプロセッサーを開発して研究に使うことにした。

この方式なら、(1)~(3)の問題はすべて解決するからだ。もちろんこの場合、既存のプログラムがそのまま動かないので、最低でもアセンブラやCのコンパイラを自前で手当てする必要があるが、実はGNU Toolchainを利用すると独自プロセッサーへのコンパイラの対応はそんなに難しくない。

最適化のレベルなどを論じ始めるといろいろ大変だが、とりあえず動くだけならばGAS(GNU Assembler)の対応をするだけで良く、これはそれほど難しくない。GASが動けばその上でGCCを動かして、ベンチマークプログラムを移植できる。

最適化を詰めるにはこれでは十分ではないかもしれないが、いざとなればハンドアセンブルでも良いわけで、研究プロジェクトとしては十分という判断である。そこで、2010年の夏から3ヵ月ほどの作業で、新しい命令セットが定められることになった。これがRISC-V ISAである。

ちなみにこのRISC-V ISAを策定したAndrew Waterman博士とYunsup Lee博士はどちらもAsanović教授の研究室の学生であり、その後は共にSiFiveを設立する。

以上のように、Raven-1はRISC-V ISAがある程度目途がついた段階で設計が開始され、2011年の5月くらいにテープアウト。GlobalFoundriesの28nm SOIプロセスで製造され、そこから本来の目的である研究プロジェクトのためにさまざまな実験が行なわれ、その結果が論文として結実するわけだが、それとは別にAsanović教授はRISC-Vでビジネス市場に持ち込むことを当初から想定していた(このあたりはHennessy教授のやり方に倣ったわけだ)。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ