Bergamoの構成を推定

1CCXあたり8コアでトータル128コアか?

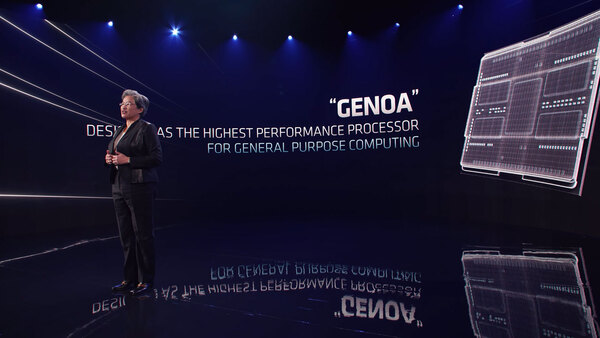

ところでプラットフォームの話だが、Genoaのパッケージ内部のCGを見る限り、12個のCCD+1個のIODという、Milan世代の基本構成は変わっていないように思える。

まだこのMilan世代のパッケージサイズなどは明らかになっていないが、現行のEPYCと大きく変わらないと考えると、ダイ1つあたりの大きさはやや小さくなっているようだ。

さて問題はBergamoの構成である。おそらくIODはGenoaと共通であろう。なので可能性としては以下の2つのパターンが考えられる。

- 1個のダイに16コアのBergamoが搭載され、これが合計8ダイで128コア

- 1個のダイに8コアのBergamoが搭載され、これが16ダイで128コア

ちなみに1つ目の場合、CCXを16コアまで増やすのか、それともCCXは8コアのまま、2つのCCXを1つのCCDに搭載するのか、という2通りの可能性があるのだが、筆者としてはダイあたり2CCX、1CCXあたり8コアという案を推したいところだ。

さすがに16ダイの搭載は実装コスト的にどうよ? という話ではあるし、そもそもTSMCのN7→N5でトランジスタ密度を倍増できるなら、高密度ライブラリーを使う前提なら、Zen 4cの16コアCCDはZen 3の8コアCCDと同程度のダイサイズに収まるだろう。

ダイとパッケージをつなぐインターコネクトのball(ダイ底面に配される、配線接続用のBGA Ball)の数を確保するためには、あまりダイサイズが小さいのは不利になる。もちろんZen 4cを他の用途(例えばデスクトップ向け)に転用するつもりなら、CCDあたり8コアに留めておく方が有利だろうが、今のところそうした計画が一切聞こえてこないあたりは、CCDあたり16コアでもかまわないように思う。

そしてCCXを1つにするか2つにするかだが、CCXあたり16コアまで拡張すると、おそらく論理設計側にも手を入れる必要があるだろう。もちろんZen 4cが「全く」論理設計に手を入れないか? というとそれはそれで難しいので若干は入るだろうが、CCXの構成そのものは少なくともZen 4/4c世代では手を入れないだろうと筆者は推定している。

以上のことからBergamoは8CCD、1CCDあたり2CCX、1CCXあたり8コアでトータル128コア、という案を提示しておきたい。このBergamo、2023年前半に市場投入とされている。物理設計に1年くらいかかるという昨今のCPUデザインの事情を考えれば、Genoaから1年遅れというスケジュールは非常に納得できるものである。

ちなみにエリアサイズがZen 4とZen 4cでは大きく変わらない(せいぜい4分の3程度)という予測が前提なので、デスクトップにZen 4cは来ないと筆者は予測している。big.LITTLEへの対応ができていないわけではない(*2)が、Armにしてもインテルにしても、bigコアとLITTLEコアの大きさが大きく異なっており、LITTLEコアはbigコアの数分の1(*3)まで縮めないとbig.LITTLEのメリットは生まれにくいように思う。

その見方でいけば、現在のZen 4cは大きすぎるように思う。ちなみに次で触れるが、Zen 4とZen 4c(というよりGenoaとBergamo)ではややSIMD命令周りに差があるかもしれない。

(*2) 例えば2019年12月にAMDは“Method of Task Transition Between Heterogenous Processors”という特許を出願し、2021年に登録されている。

(*3) Alder Lakeで見る限り、E-CoreはP-Coreの4分の1くらいのエリアサイズに見える。

この連載の記事

-

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ - この連載の一覧へ