ロードマップでわかる!当世プロセッサー事情 第640回

AI向けではないがAI用途にも使えるCoherent LogixのHyperX AIプロセッサーの昨今

2021年11月08日 12時00分更新

MNP(Memory-Networked Processing)アーキテクチャーは

メモリーと演算ユニットを格子状に配置して重ねる構成

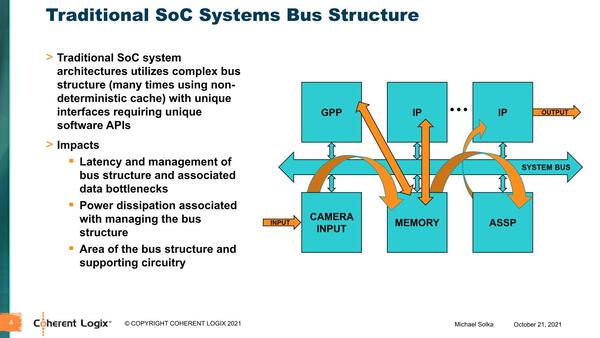

Linley Processor Conferenceでの説明は、それではMNPとはなにか? という話から入る。既存のアーキテクチャーは大抵の場合Unified Memory、つまりメモリーシステムは1ヵ所にまとまり、ここにシステムのその他のユニットからアクセスされる形をとる。この結果としてこのメモリーシステムがシステム全体のボトルネックになるという話だ。

単に帯域だけではなくレイテンシーも増えやすいし、広帯域/低レイテンシーなバスは消費電力、エリアサイズともに大きくなる。最近CPUが大容量キャッシュを搭載するようになったのも、メモリーシステムそのものがシステムの要求に追いつかなくなってきたため、これを緩和するためという用途に加え、バスネックを少しでも減らしたいという目的もあることを考えれば、少なくともこのスライドの言っていることは正しい。

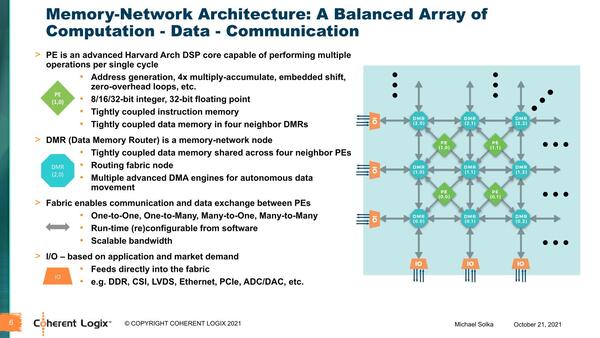

この問題を解決するために、MNPではメモリー(DMR)と演算ユニット(PE)をそれぞれ格子状に配置して重ねるというおもしろい構成を取っている。PEは隣接するDMRからデータを取得し、演算結果はまた隣接するDMRに送り出す形になる。DMRは自身もメモリーを持つとともに、自身にないデータは隣接するDMRから取得する(逆にPEから格納された演算結果を必要に応じて別のPEに送り出す)という仕組みになっている。

外部メモリーもI/Oの扱いになっており、使い方としては煩雑にメモリーアクセスするというのではなく、必要に応じてブロック単位で読み込み、各DMRに分散させて格納。PEはあくまでもDMRしか見ずに演算するという、昨今のAIプロセッサーと同じ仕組みになっている。

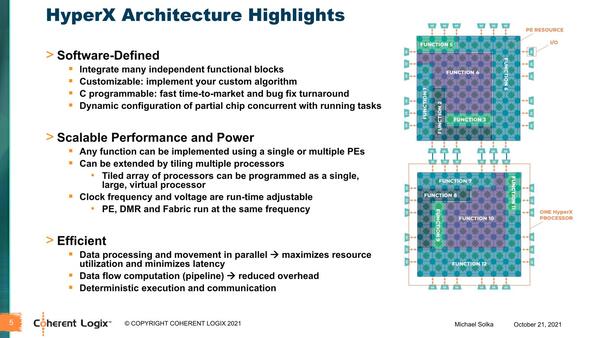

スライドが前後するが、このMNP構成の演算ユニットをまとめたものを、同社ではHyperXアーキテクチャーと称している。おもしろいのは、このPEをどう組み合わせるかを自由に定義できることだ。

各PEはそれぞれ独自にInstruction Memoryを保持しているので、PE単体でももちろん動作するが、複数組み合わせて機能ブロック(Function Block)を構成することもできる。このブロックをどう組み合わせるかはプログラマーが定義でき、なんなら稼働中にブロック構造を動的に変更することも可能とされる。さらに上図にあるように、I/Oを経由して複数のHyperXチップを結合することも可能である。

ところでこの構図、「DMRからデータが取れる、あるいはDMRに結果を書き出せる」時はPEは稼働し、「データが来てない、もしくはデータを書き込めない」時にはPEが止まることになる。つまりデータの有無で動作制御できるわけで、事実上のデータフロー構成のプロセッサーとして稼働しているわけだ。このあたりの特徴だけ見ると、昨今のAIプロセッサーそのものという感じである。

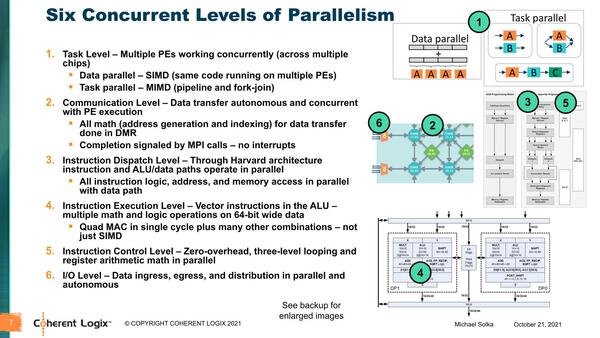

ちなみに同社によれば、HyperXは6レベルの並列性があるとしている。まずブロック単位の処理(=タスク)で言えば、1つのブロックに複数のPEを含めるので、SIMD的な処理も可能で、個々のPEで別々の処理もできるから、その場合はMIMD動作になる。

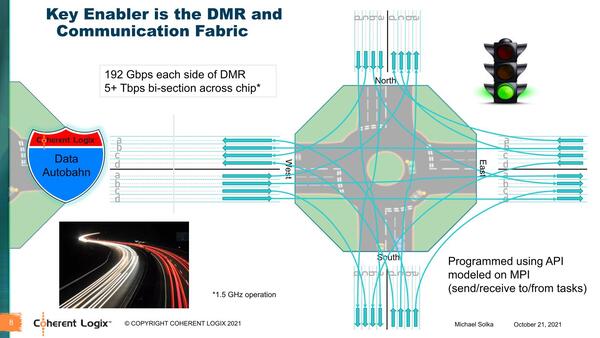

またPEの稼働にともなう通信は全自動で行なわれ、PE内部も複数の同時処理が可能(SIMD演算を含むVILW命令)で、I/Oも複数を同時に動作できる。これを支えるのはDMR同士の通信であるが、リンク帯域は1方向あたり192Gbpsに達し、チップ全体では5Tbit/秒以上の帯域を誇ることになる。

この連載の記事

-

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 -

第847回

PC

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手 -

第846回

PC

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ -

第845回

PC

最大256MB共有キャッシュ対応で大規模処理も快適! Cuzcoが実現する高性能・拡張自在なRISC-Vプロセッサーの秘密 -

第844回

PC

耐量子暗号対応でセキュリティ強化! IBMのPower11が叶えた高信頼性と高速AI推論 -

第843回

PC

NVIDIAとインテルの協業発表によりGB10のCPUをx86に置き換えた新世代AIチップが登場する? -

第842回

PC

双方向8Tbps伝送の次世代光インターコネクト! AyarLabsのTeraPHYがもたらす革新的光通信の詳細 - この連載の一覧へ